# IGBT開発の経緯(前)

## 中川 明夫 (㈱東芝 セミコンダクター社 首席技監)

## 1.はじめに

「半導体」と聞くと、多くの方はICを想像されると思いますが、ここでご紹介するのは「パワー半導体」と呼ばれるもので、ICよりも高い電圧、大きな電流を扱える半導体です。そのひとつの代表がIGBTと呼ばれる素子です。IGBTはパワーMOSFETと並びパワーエレクトロニクスの世界ではなくてはならない素子としているいろな分野に使われています。鉄道や新幹線、エアコン、洗濯機、IHクッキングヒータなどの家電製品、エレベータ、直流電力送電、太陽光発電、風力発電、そしてハイブリッド車などその応用はエネルギー変換全般に及びます。カバーする電流は10Aから数百アンペア、電圧は600Vから6000Vにもなります。

このIGBTはその概念の提案、誕生から25年あまりしかたっていない新しい素子です。私は幸運にもその初期の開発、誕生にかかわって来ました。その開発の経緯を述べてみたいと思います。

## 2. ノンラッチアップIGBT開発の背景

私がIGBTの開発を始めたのは1983年3月です。1984年12月、米国の電子デバイス国際学会IEDMで世界で初めてのラッチアップしないIGBTを論文発表しました1)。それを契機に、IGBTはバイポーラトランジスタやGTOを置き換える素子として急速な発展を遂げました。

1980年初頭、米国ではバイポーラトランジスタを MOSゲート駆動できないか、あるいはバイポーラト ランジスタ並みの電流駆動能力があるMOSゲート素

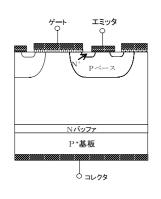

図1 IGBTの構造

子ができないかという ような模索が真剣に検 討されていました。印 象に残っているのは 1981年にGEのAdlerが PESCで発表した、バイ ポーラトランジスような 組み合わせが優れてい るかを検討した論文で す<sup>2</sup>)。バイポーラとMOSを組み合わせた素子は当時BiMOSと俗称されていました。一方、この当時の日本ではGTOサイリスタの開発が成功し、その開発が華やかであった時期です。このような背景の中、IGBTの実現に向けた動きが米国で始まります。その基本動作原理はHans Becke等が1980年に特許を申請し<sup>3</sup>)、1982年にはBaligaが最初の素子の試作結果をIEDM<sup>4</sup>)で、1983年にJ. P. RusselがEDLに論文発表<sup>5</sup>)するなど米国でIGBT開発の動きが活発化します。

IGBTはMOSゲートで大きな電流をスイッチングできるという特徴がありますが、素子内部に持つ寄生のサイリスタがラッチアップしてしまうという問題は当時解決できない難問であると考えられていました。

サイリスタを構成するNPNトランジスタの動作を抑え、NPNのPベース上にゲートを設けてNMOSとして動作させ、そのドレイン電流でPNPトランジスタのベース電流を供給する構造としたものがIGBT(図1)であり、構造的にはMOSサイリスタと同一となっています。IGBTの開発に従事していた研究者は皆が寄生のサイリスタのラッチアップの抑制は不可能に近いと思っていたのです。そのため多くのメーカがIGBTの開発に躊躇していました。その中でNon-Latch-Up IGBTが日本で開発されたのです。ラッチアップしないIGBTを実現してみると後述するようにIGBTが当初想定した以上に優れた素子であるということがわかったのです。

#### 3.IGBTの幸運

当時、IGBTの開発をする中で、システム側からはバイポーラトランジスタを置き換えるためにはバイポーラトランジスタが既に実現している負荷短絡耐量<sup>1)</sup>を持たなければいけないといわれました。負荷短絡耐量とは動作中に負荷が短絡し、電源に素子を直結した状態となり、この状態で素子がオンしても壊れずに持ちこたえる能力です。素子の電圧降下はオン状態であっても電源電圧と同じ数百ボルトにもなり電流は流れるだけ流れるという状態で20µsec程度破壊せずに持ちこたえなければならないのです。電流密度は

1000A/cm<sup>2</sup>を超えますので損失は300kW/cm<sup>2</sup>以上にも達します。寄生のサイリスタのラッチアップを抑えたIGBTは実にこの過酷な負荷短絡にも耐えることが実証できたのです。これによってIGBTはバイポーラトランジスタの完全な置き換えへと繋がって行きます。

一旦、ラッチアップの抑制に成功してみると他にもIGBTの良い点がたくさん見えてきました。その一つは想定以上に破壊に強く、大きな電流を遮断できるということです。今までは簡単に破壊する素子というのがIGBTのイメージであったわけですが、ラッチアップを防いだ素子は逆にバイポーラトランジスタ以上に強い素子に変貌したのです。6)。

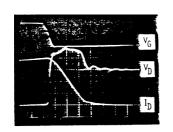

バイポーラトランジスタには避けられない欠点がありました。よく知られた2次降伏7)(Second breakdown)です。この2次降伏があるため最大の電力損失は200kW/cm²を超えることができません。最初に開発したIGBTの電力損失は125度で300kW/cm²、常温で400kW/cm²に達し、最初の負荷短絡試験で既にバイポーラトランジスタの限界を超えてしまったのです。また、IGBTには自己クランプ能力があり、アバランシェ領域に突入しても図2に示すように自己クランプし、保護回路なしでインダクタンス負荷でのターンオフができたのです¹)。その後、何故IGBTは強いのかということを研究課題にあげたほどです8)。

バイポーラトランジスタの2次降伏はコレクタ電流を流すのが電子のみであるというところにあります。電流密度が上がるにつれて電子の量が増え、電子密度がドレイン高抵抗層の不純物濃度を超えてしまうと、電子が持つ負電荷が高抵抗N形層のドナーの正電荷を上回り電荷の総量が正から負に変わるため高抵抗N層と高濃度N+ドレイン層の境界に高電界が生じて2次降伏が起こります。IGBTは電子と正孔の両方が電流を担うため互いに電荷を打ち消しあい、バイポーラトランジスタのように電子の負の電荷が見えてくるということが基本的に起こりません。したがって高電流が流れ

Fig.4 Typical inductive load switching waveform. Ip:12A/Div, Vp:200V/Div Time:0.5psec/Div.

図2 自己クランプするIGBTの ターンオフ波形

ても局部的に高電界層 ができるということが なく、大電流、高電と の状態を維持できるの です。これは最大を 電流が大きく、安全に 動作する電流電圧の範 囲が広いという特徴に なって現れてきます。

しかし、最初に開発

したIGBTはまだバイポーラトランジスタに対して完全に優位に立てたわけではありません。それは電圧降下や、スイッチングスピードがまだバイポーラトランジスタに比べて見劣りしたためです。これらの特性はその後の素子作成プロセスの微細化によって特性が改良されて行くことになります。

## 4. BaligaのIGRの論文に接して

私がIGBTに初めて接したのは1982年の半導体素子 で最も権威ある学会である米国IEDMでのBaligaの IGR4)という素子の発表を聞いたときです。当時はま だIGBTという素子の名前はなく、各社が勝手な名前 で呼んでいました。GEはIGRやIGT、RCAはCOM-FET 5 、 当社はバイポーラ形 MOSFET ( Bipolar-mode MOSFET )1,9)と呼びました。当時のBaligaの論文発表 の印象を今でも覚えています。それはすごいという印 象ではなく「何故このような遅い素子を発表するの か」という驚きでした。確かにサイリスタ構造を持ち ながらMOSゲートでターンオフできるというのは新規 性がありますがターンオフタイムが10µsecというのは いかにも見劣りしました。実は負け惜しみかもしれま せんがIGRのような構造にすればMOSゲートで電流を 扱えそうだというのは1980年頃にパワーMOSFETを開 発していたときアイデアとして考えたことがあったの です。しかし、内部に電子や正孔が多量に蓄積するた めターンオフがMOSFETと比べて極端に遅くなり使え ないと思い込み、真剣には考えませんでした。「やっ ぱり遅いじゃないか」というのが率直な感想なのでし た。しかし、帰国後、IGRと同じ素子を開発すること になるのは、少しくらいスイッチングスピードが遅く ても大電流の応用が実はたくさんあるとわかったから でした。正に応用について良く知らなかったのです。

## 5.米国留学とデバイスシミュレータの開発

1981年9月よりマサチューセッツ州立大学のNavon 先生の元に滞在し、2次元のパワーデバイスシミュレータを開発していました。1980年代、デバイスシミュレータはLSIの分野で大きく発展しており、CMOSの特性解析に使われようとしていました。NMOSやPMOSでは基本的に電子または正孔電流しか流れず、いずれか一方の電流の方程式を解けば特性が求まりましたが、パワー素子はGTOやバイポーラトランジスタなどが一般的で、電子と正孔の両方を扱う必要があり、また、300V以上の高電圧をも扱うという二重の困難を抱えていました。デバイスシミュレータは素子の不純物分布

やその構造を入力すれば素子の特性を計算でき、現在では半導体素子設計に不可欠のツールとなっています。

当時Navon教授の研究室で、パワー素子を約1000の 格子に分割して微分方程式を差分方程式に変えること で3千の非線形連立方程式を解くことに挑戦しました。 ニュートン法を用いることで線形化し、繰り返し収束 計算を行うことで連立方程式を解くことを試みました がすべて破綻しました。窮した挙句、ガウスの消去法 が頭に浮かびました。数の少ない連立方程式なら迷わ ず選ぶガウスの消去法ですが、3千の連立方程式で係数 の大きさも20桁以上異なり、有効数字が16桁しかない コンピュータでガウスの消去法は桁落ちが起こるため 使えないとされてきました。しかし、足し算、引き算 はディメンジョンが一致した数値同士で行われるため 桁落ちは影響がないと考え、ガウスの消去法を試みた のです。結果は上手くいきました。今まで求まらなか ったGTOのターンオフの計算ができるようになったの です。これを論文にまとめて1982年のIEDMに臨みま した<sup>9</sup>)。そこで出会ったのがBaligaのIGRの論文でした。

# 6. ノンラッチアップIGBTの開発

1983年2月末に日本に帰国して見ると、光でMOS-FETとバイポーラトランジスタの複合素子を駆動する という仕事を大橋氏が始めていました。光をダイオー ドで受け電圧に変え、これでMOSFETを駆動するとい うもので、大電流を扱えるようにMOSFETで更にバイ ポーラトランジスタを駆動するというものでした。私 を待っていた仕事はMOSFETとバイポータトランジス タを1チップ化することでした。この仕事は魅力があ りませんでした。技術の先が見えている。それより も、先は見えないが可能性がある仕事が良いと即座に 思いました。そしてBaligaが発表した素子の理想形を 目指すことにしました。IGRはサイリスタの動作に似 ており、NPNとPNPの組み合わせをNMOSとPNPの 組み合わせに変えたに過ぎず、サイリスタ同様高耐圧 化が可能と考えました。これはMOSとバイポーラト ランジスタの組み合わせで、1400Vという限界が見え ていたバイポーラトランジスタよりも高耐圧化できる 可能性がありました。高速化もまだこれからでした。

早速試作に取り掛かりました。米国勢をキャッチアップするためラッチアップ耐量の増大と高速化に最初のターゲットを置きました。(1) Nソース層の下に設ける浅いP+拡散、(2) 最適エミッタパターン、(3) 薄いN+バッファ構造、(4) 電子線照射の4つの実現を目指しました。素子の試作は存外にスム

ーズに進みました。それは基板ウェハを除けば試作プロセスはパワーMOSFETとほぼ同じであったからです。NチャネルMOSFETのソースがNエミッタとして働かないようにするため、ソース層の下に浅い高濃度P形層を拡散するなど当時からすれば斬新なアイデアを盛り込みました。特筆すべきは2次元のデバイスシミュレータで解析しやすいようにストライプのパターンを入れたことが幸運になりました。これが意外とラッチアップ抑制に効果があったのです。

次の課題は基板ウェハの入手です。高濃度のP形 基板ウェハに低濃度のN形の層をエピタキシャル成 長させる必要があります。また、高耐圧化・高速化 するためP基板と低濃度高抵抗のN層の間に高濃度 のN+層を挟む必要があります。当時、エピウェハは 社内で内製しており、専門の課がありました。ウェ 八作成の相談に行きましたが、高濃度P基板の上にN 形層の形成は先例がなく断られました。しかし、話 をするうちに次のようにすれば可能なことが解りま した。まず、高濃度P基板に低濃度P層を数ミクロン 形成してもらう。これにAsをイオン注入して拡散 し、表面に薄いN形層を形成する。一旦、表面がN 形にできればその上に低濃度高抵抗のN形層を50µm 形成してもらえることになりました。これでウェハ が入手でき、しかも薄い高濃度N+層も可能となった のです。その結果1983年10月頃最初の試作が終わり 非常に良好なIGBTが最初のロットで実現できまし た。しかし、同年12月のIEDMでRCAに薄いN+バ ッファを先に発表されてしまいます10%(つづく) 参考文献

- 1 ) A. Nakagawa et.al., IEEE IEDM Tech Digest, p.860 (1984)

- 2) M. S. Adler, 1882 PESC Record, p.371

- 3) H. W. Becke, Carl F. Wheatley, Jr. USP 4364073

- 4) B. J. Baliga, et al, IEEE IEDM Tech. Digest, p. 264 (1982)

- 5 ) J. P. Russell, et al, IEEE EDL, EDL-4, p. 63(1983)

- 6 ) A. Nakagawa et. Al., IEEE Trans. Electron Devices, ED-34, p.351 (1987)

- 7) P. L. Hower et. al., IEEE Trans. Electron Devices, vol.ED-17, p. 320

- 8 ) A. Nakagawa, PESC'88 Record, p84

- 9) A. Nakagawa et. al., IEEE IEDM Tech. Digest, pp.496-499 (1982)

- 10 ) A. M. Goodman et al., IEEE IEDM Tech. Digest, p.79 (1983)