## 65ナノ時代のシリコン材料技術

久保田 裕康 (東芝セラミックス株)

メモリやMPUに代表される半導体デバイスは3年で一世代のスピードで微細化しており、現在、既に90nmの量産が始まっている。65nmについても開発が進められており、2~3年後には量産が開始されると予想されている(図1)。デバイスの微細化に伴い、基板として使用されるシリコンウェーハにはより一層の高品質化が求められている。また、デバイスの高性能化のためにSOIや歪みシリコンといった新しいシリコン材料が一部の半導体メーカで既に量産に使われ始めている。ここではこのような状況を踏まえながら65nm世代に向けたシリコン材料の動向について概説する。

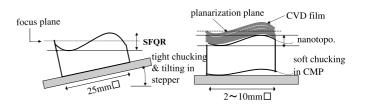

1.超平坦化のために「両面ミラー」の採用へ 微細リソグラフィ技術とウェーハ平坦度は切って も切れない関係にある(図2)。ウェーハに必要とされる平坦度は、リソグラフィに用いられるステッパ (露光装置)のDOF(Depth of Focus)から逆算される。 露光時のウェーハ表面の凹凸は、ウェーハ自身の平坦度は勿論、デバイス工程で生じる段差や、リソグラフィプロセスのバラツキ、ウェーハチャックの平坦性等により影響を受けるが、これらバラツキをすべて含んだものがDOFの範囲内に収まらなければならない。経験的にはウェーハ自身の平坦度は概ね DOFの1/3~1/4以下が必要とされており、デザインルール(最小パターン寸法)とほぼ同等となる。現

在広く使われている「片面ミラー」ウェーハはラッ ピング後、加工歪み層を取り除くためエッチングを 行うが、裏面はこのエッチング面がそのまま現れて いる。裏面が粗れていると平坦度向上には限界があ るため、65nm世代ではより高平坦化が可能な「両面 ミラー」ウェーハが主流になると考えられる。 300mmウェーハでは、既に両面ミラーが世界的に標 準仕様となっているが、200mmウェーハでも65nm世 代からは両面ミラーの採用が本格化しよう。両面ミ ラーではラッピングに代わって平面研削を用いて厚 さの均一性を図るとともに、破砕層を浅くしてエッ チング工程を省略し高平坦度化に対応する検討も行 われている。また、デバイス形成領域をウェーハ面 内最大限拡大してチップグロス数を増やすため、ウ ェーハ周辺の平坦度の保証外領域(エッジカット) を2mm、更には1mmへと縮小してゆく要求が出てき ており、ウェーハメーカーにはウェーハ最外周まで 含めた超平坦加工技術の開発が望まれている。

図2 リソ対応の平坦度(SFQR)とCMP対応Nanotopo.

| Year of Production                                            | 2003   | 2004   | 2005  | 2006  | 2007  | 2008  | 2009  | Driver |

|---------------------------------------------------------------|--------|--------|-------|-------|-------|-------|-------|--------|

| Technology Node                                               |        | hp90   |       | 200   | hp65  |       |       |        |

| DRAM ½ Pitch (nm)                                             | 100    | 90     | 80    | 70    | 65    | 57    | 50    | D 1/2  |

| MPU/ASIC Physical Gate Length (nm)                            | 45     | 38     | 32    | 28    | 25    | 23    | 20    | M      |

| Wafer diameter (mm) **                                        | 300*** | 300*** | 300   | 300   | 300   | 300   | 300   | D ½, M |

| Edge exclusion (mm)                                           | 2      | 2      | 2     | 2     | 2     | 2     | 2     | D ½, M |

| Front surface particle size (nm), latex sphere equivalent [D] | ≥90    | ≥90    | ≥90   | ≥90   | ≥90   | ≥90   | ≥90   | D ½, M |

| Particles (cm <sup>-2</sup> ) [E]                             | ≤0.35  | ≤0.35  | ≤0.35 | ≤0.18 | ≤0.18 | ≤0.09 | ≤0.09 | D 1/2  |

| Particles (#/wf)                                              | ≤238   | ≤238   | ≤241  | ≤123  | ≤123  | ≤63   | ≤63   | D 1/2  |

| Site flatness (nm), SFQR 26mm × 8mm site size [F, R]          | ≤101   | ≤90    | ≤80   | ≤71   | ≤64   | ≤57   | ≤51   | D ½, M |

| Nanotopography, p-v, 2mm diameter analysis area [Q]           | ≤25    | ≤23    | ≤20   | ≤18   | ≤16   | ≤14   | ≤13   | М      |

また、最近ではデバイスプロセスへのCMPの導入 に伴い、nanotopographyと呼ばれる新たな平坦度が ウェーハ規格に導入され始めている。CMPはウェー 八を比較的自由な状態で保持し、ウェーハ表面の金 属配線膜や層間絶縁膜等を研磨布で研磨、平坦化す るもので、ウェーハ表面の凹凸に応じて金属膜や絶 縁膜の厚さムラを引き起こす。リソグラフィから要 求される平坦度はウェーハ裏面強制吸着状態でのウ ェーハ表面の凹凸であるが、CMPから要求される平 坦度(nanotopography)は、ウェーハを吸着しない自 由な状態でのウェーハ表面の凹凸といえる(図2)。 層間絶縁膜のバラツキは寄生容量のバラツキとなっ てデバイスの動作周波数に影響するため、一部のデ バイスメーカではnanotopographyをウェーハ規格に 導入している。今後、デバイスの高速化が進むにつ れnanotopographyを規格化するメーカが増えてくる ものと考えられる。

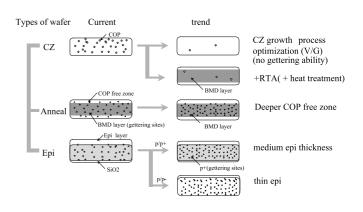

## 2. バルクシリコンウェーハは「無欠陥CZ」 「アニール」、「エピ」の棲み分けに

通常のシリコン結晶中には、酸素析出物や空孔の集合体であるボイド状欠陥(COP)が、それぞれ~ $10^8$ ケ/cm³、~ $10^6$ ケ/cm³存在する。これらの欠陥は、ゲート酸化膜の耐圧劣化や接合リーク電流の増大を引き起こすこと等から、ウェーハ表面からデバイス形成深さまでは完全に除くことが望ましい。デバイス形成深さは素子構造によって異なるが、トレンチ型のDRAMではキャパシタに深いトレンチが使われることから~ $10\mu$ 、一方、スタック型DRAM、あるいはロジックデバイスでは~ $3\mu$ 程度が欠陥フリーとすべき深さの目安となる。特にモバイル用途の半導体では待機時の消費電力を抑える必要性からリーク電流の許容値は厳しくなる一方で、従来にも増してデバイスの形成領域の無欠陥化が重要になっている。

シリコンウェー八の表層無欠陥化を実現する方法として、現在では、大別して1)無欠陥CZ、2)高温アニール、3)エピ、の三つが実用化されている(図3)、「無欠陥CZ」は、CZ引き上げ条件を最適化して、COPの形成を結晶段階で抑制する取り組みである。COPは、結晶引き上げ時に、固液界面から導入された過飽和な原子空孔(vacancy)が、その後の結晶の冷却過程で凝集した0.1~0.2μmの正八面体をしたボイド(空隙)である。COPの形成過程を支配するパラメータとして、結晶の引き上げ速度(V)と結晶の温度勾配(G)の比V/Gをある一定の範囲に制御すると

COPが全く形成されないことが判明している。結晶全体(長さ方向、及び径方向)に亙ってこの範囲に制御する事でCOPの無い結晶が作成できる。課題はいかに結晶全域にわたってV/Gを一定に制御するかということであり、シリコンメーカー各社は各種の工夫、検討を進め、200mm結晶については既に量産化されており、300mmについても量産の段階に入りつつある。但し、引き上げ速度は通常より概ね遅く、結晶の生産性は低下する。生産性を含めコスト上昇をいかに抑制するかが今後の課題である。また、無欠陥CZは、酸素析出物も少なくゲッタリングリ能力がないため、デバイス製造ラインとのマッチングが重要となろう。

高温アニールは、通常のCZウェーハを、水素やアルゴンなどの還元性あるいは不活性雰囲気中で高温熱処理(アニール)することにより、ウェーハ表層部からCOPを消滅させる方法で、水素アニールウェーハがその代表である。最近では、窒素等の不純物を結晶引き上げ時にドーピングすることにより、CZ結晶のCOPのサイズを極力小さくする事で、高温アニール処理でのCOPの消滅効果を高め、表層~5μ深さまでCOPがほとんど消滅したウェーハが量産化されている。アニール工程では、同時に内部に酸素析出物(BMD)が形成され、BMDはデバイス工程での金属汚染のゲッタリングサイトとなるため、「表層無欠陥、内部にはゲッタリング層」と理想的なウェーハ構造が実現される。現在、200mmでは勿論のこと、300mmでも量産されている。

エピウェーハは通常CZ基板の上に、CVD法を用いてエピタキシャル層を形成するもので、エピ層自身はCZ結晶では不純物として含まれる酸素やCOPもなく、結晶品質的には理想的と考えられている。更に、p/p<sup>+</sup>といった構造が容易に作れるため、ラッチアッ

図3 バルクシリコンウェーハの流れ

プやソフトエラー耐性などのデバイス信頼性を向上させる効果も発揮でき、高性能のMPU等で使用されている。エピ成長は通常枚葉CVD装置を用いて行われるが、p/p<sup>+</sup>ではエピ成長中のオートドープ抑制のため裏面をCVD膜でシールすることを含めてコストが高いのが難点である。最近では、p/p<sup>-</sup>構造のエピとしてコストを下げる取り組みがなされ、実用化している。

「無欠陥CZ」、「アニール」、「エピ」はそれぞれ特徴があり、これらのウェーハはいずれも200mmはもとより300mmの先端デバイスで量産に使われている。デバイスメーカもウェーハ物性のどこに重点を置くかでウェーハ選択の基準が異なるため、今後もこれらのウェーハは棲み分けられながら使われてゆくことになろう。

## 3.バルクシリコンに加え、「SOI」、 「歪シリコン」、「SGOI」等が 本格実用化を迎える

上述のシリコン・バルクウェーハに加え一部の高性能デバイスではSOIや歪みシリコン等の新しい構造の基板を使う動きが出ている。

「SOIウェーハ」を用いるとデバイスの寄生容量が低減し、低消費電力化、高速化が容易に実現でき、携帯通信用ICやMPUなどの一部に量産採用されている。これらに使われるSOIウェーハは、SOI層の厚さが~ $0.2\mu$ 以下と薄く、その製造方法としては大別してSIMOX、貼り合わせの2系統に分かれる。SIMOXはSOI層の膜厚均一性が貼り合わせ法に比べて優れるが( $\pm 2\%$ )、SOI層に貫通転位、埋め込み酸化膜にはピンホールなどの欠陥が残存するという欠点がある。貼り合わせ法はSOI層の結晶品質、及び埋め込み酸化膜(Box)の耐圧特性がSIMOXに比べて優れるという特徴がある反面、膜厚均一性はSIMOXに比べてやや劣る。いずれも、300mm径まで実用化、量産されているが、現状では貼り合わせ法の方が優勢のようである。

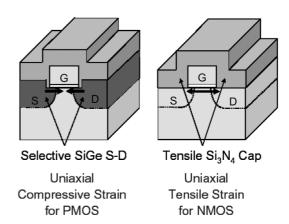

「歪みシリコン」は、シリコンの格子を伸ばした り圧縮することにより、電子やホールの移動度を向 上させ、デバイスの特性(スピード)を向上させる ためのものである。たとえばSiより格子定数が4.2% 大きいGeを数%~数十%程度混ぜたSiGe結晶層をSi 基板上にヘテロエピ成長させ、その上にノンドープ Si層(歪みシリコン)を数十nmエピ成長させると引 っ張り応力を与えられ、電子の移動度を向上させる

図4 Intel社の90nm世代用歪みシリコントランジスタ (同社ホームページより)

ことができる。この歪シリコン層をチャネル層にす ることで高速なn-chトランジスタが出来る。また、 逆にホールの移動度は格子を圧縮することにより上 昇することから、SiGeの選択エピを行いp-ch部のシ リコン領域を圧縮すると同時に、n-ch部のシリコン 領域を伸ばしてCMOSテバイス全体の高速化を図っ ているメーカもある(図4)。これら歪シリコン材料 を導入することにより、一世代先の微細化プロセス での性能を実現できるため、テバイスメーカでの関 心は最近急速に高まってきている。また、SOIと歪 みシリコンを組み合わせた絶縁層上の歪みシリコン (SGOI)の研究開発も国プロとして行われている。 半導体デバイス全体を見たときには、SOIウェーハ や歪みシリコン、あるいは更にSGOIがシリコンバル クウェーハにとって替わることはないと考えられる が、超高速や超低消費電力を志向した最先端のデバ イスには今後、これら「新シリコン材料」が確実に 採用されてゆくだろう。

## 4.まとめ

シリコンウェーハは、半導体デバイスを製造する上で、依然として主流の座を持ち続ける重要な基板材料である。65nm世代のデバイスの高集積、高機能化に対応して、品質的には超平坦化、無欠陥化が徹底的に追求される。また、薄膜SOIウェーハや歪みシリコンがシリコンバルクウェーハの限界を打ち破る材料として先端デバイスではより普遍的に使われるようになろう。微細化を従来と同等のスピードで進めるには、リソ技術をはじめとした半導体プロセスの課題を解決してゆかなければならないが、基板となるシリコンウェーハの進化も必須条件であり、従来以上にその役割は重要になると考えられる。