## September 1969 Invention of the DSA MOSFET (Electrotechnical Laboratory) ~ Discrete Semiconductor/Others ~

For the high speed and high frequency operation of MOSFET, shortening of the gate length is required. In order to realize high speed and high frequency operation, a short channel gate of 1µm or less is required. However, at the time, the minimum processing size was 5-7µm in the contact lithography era. For this reason, several MOSFET structures that realized a short channel gate by a method other than lithography processing were devised.

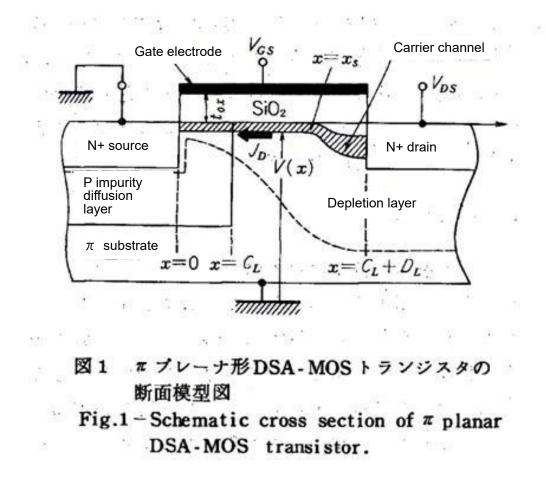

Tarui et al. of the Electrotechnical Laboratory devised DSA (Diffusion Self-aligned) MOSFET, by the application of double diffusion technology used for bipolar transistors in which emitter and base were formed simultaneously. In this method, base forming impurity and emitter forming impurity were simultaneously diffused, in the optimized conditions of diffusion coefficient difference, surface concentration difference, diffusion temperature and time. P-type impurity and n-type impurity were diffused from source diffusion window on the n-type substrate, thereby forming p-layer and n-layer (refer to Fig.1). Since the diffusion depth of impurity can be controlled with the accuracy of less than 1µm, MOSFET with much shorter channel length than the one fabricated by lithography method could be made. It came to be called D-MOS (Double-diffused MOS Transistor) at IEEE.

Tarui et al. observed high-speed switching with tp=1.2ns (tpp=2.5pJ) in a submicron channel E-D DSAMOS FET ring oscillator. Furthermore, H. J. Sigg et al. of Signetics realized a DSAMOS FET with a channel length of 1.3µm, f<sub>max</sub>=10GHz, gain=7dB (at 2GHz). It was a revolutionary value at that time. High speed operation of the DSAMOS FET was greatly expected as a logic LSI and the development was promoted. Mitsubishi Electric's Tomizawa et al. developed a 920 gate E-D type master slice and realized an operation speed of 3ns. However, after that, as the lithography technology advanced and CMOS emerged, the superiority of DSAMOS was lost. Rather, by the characteristics of DSAMOS suitable for high-voltage operation, it has developed as a power MOSFET. Recently, SiC DMOS FET with 1200 V breakdown voltage has been developed.

## References:

- (1) Y. Tarui, Y. Hayashi, & T. Sekigawa, "Diffusion Self-Aligned MOST: A new approach for high speed device," in Proc. 1st Conf. Solid State Devices, Tokyo, Japan, (Sept. 1969)

- (2) Y. Tarui, Y. Hayashi and T. Sekigawa, "DSA enhancement-depletion MOS IC," IEDM Digest of Tech. Papers, pp. 110, (Oct. 1970)

- (3) H. J. Sigg, G. D. Vendelin, T. P. Cauge, & J. Kocsis, "D-MOS Transistor for microwave applications," IEEE Trans. Electron Devices, Vol. ED-19, pp. 45-53, (Jan. 1972)

- (4) O. Tomisawa, K. Anami, M. Nakaya, M. Ohmori, I. Ohkura, & T. Nakano, "A 920 gate DSA MOS masterslice," J. Solid-State Circuits, Vol. SC-13, pp536-541, (Oct. 1978)

- (5) K. Nakagawa, T. Ashida, H. Takeuchi, & K. Fujii, "A 1000V high voltage p-channel DSAMOS-IC," IEDM Digest of Tech. Papars, pp. 72-75, (Dec. 1982)

- (6) Stalter, O. Burger, B. Lehrmann, S. ,"Silicon Carbide (SiC) D-MOS for grid-feeding solar-inverters" 2007 European Conference on Power Electronics and Applications, pp.1-10, (Sept. 2007)