## 1988 <u>Start of LOC structure development</u> ~ Packaging ~

In 1988, Hitachi announced its activity of LOC (Chip On Lead) technoogy development as a high density packaging technology for DRAM in the May issue of the Nikkei Microdevice, and explained the outline of the technology in August in the same year in Hitachi Review.

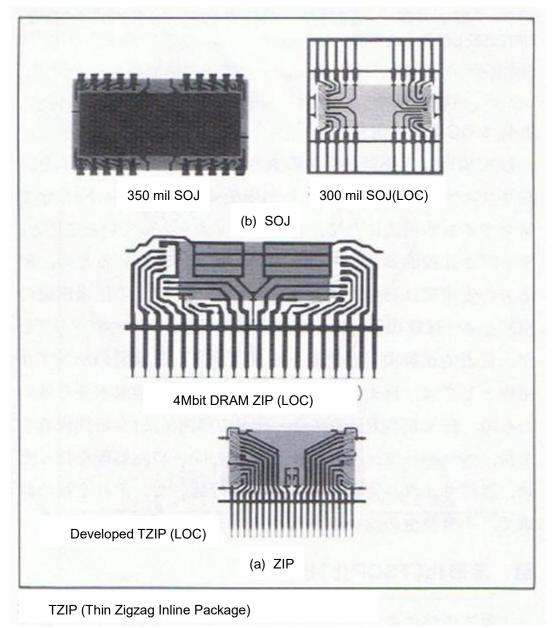

The LOC structure was put to practical use test in SOJ and ZIP (Zigzag In-line Package) of 4 MDRAM, as it could store larger die size component in the same small package outline, and was superior in environmental reliability and electrical characteristics as well, compared with the conventional structure.

Thermoplastic polyamide is attached to both sides of polyimide base material, which is first glued to lead frame, and a DRAM chip is die-bonded to the other side by a newly developed LOC mounter. After that, it is processed in the conventional assembly and mold technology.

| 項             | 8                    | Conventional                                   | COL                        | LOC                                                 |

|---------------|----------------------|------------------------------------------------|----------------------------|-----------------------------------------------------|

| Structure     | Description          | LSI pellet<br>Au wire<br>Die pad<br>Lead frame | LSI pellet                 | Lead frame Insulating<br>film<br>LSI pellet Au wire |

| Lead<br>frame | Die pad              | Yes                                            | No                         | No                                                  |

|               | Insulating<br>film   | No                                             | Yes                        | Yes                                                 |

| Wire bond     | 2 <sup>nd</sup> bond | 4 sides of chip                                | 2 sides of chip            | All inside the chip area                            |

|               | 長き(mm)               | 2.0~3.0                                        | 20~25                      | 0.2-2.0                                             |

| Die bond      | Large die            | Stress unbalance betw. leads                   | Stress relief by ins. film | Stress relief by ins. film                          |

| 大ペレット, 収納化率   |                      | Δ                                              | 0                          | 0                                                   |

| 最大男子互納率       |                      | 00%                                            | 70%                        | 90%                                                 |

| 美 逸 化         |                      | 0                                              | 0                          | 0                                                   |

| マルテ電源化        |                      | Δ                                              | Δ                          | 0                                                   |

| 信 親 は         |                      | 0                                              | 0                          | Ô                                                   |

| 性资的群易度        |                      | 14                                             | *                          | *                                                   |

Comparison of COL/LOC package structures: Large dies can be mounted and multi power sourcing can be provided by LOC structure, thereby realizing higher speed.

注:略語説明など COL (Chip On Lead)。LOC (Lead On One)、メリット大○→○→△小

Example of 4M DRAM adopting LOC structure (X-ray photograph)

In LOC structure, all the wires are bonded within the die area, and it becomes possible to mount large dies in small packages.

Version 2019/1/31