2017年

125℃動作FeRAM 量産開始(RAMXEED)

~集積回路~

1987年頃Ramtron が発表した、強誘電体薄膜をもちいる不揮発性メモリFeRAM(Ferroelectric Random Access Memory)は、原理的にはDRAMと同等の高速動作で高記憶密度のメモリを実現する可能性があり、究極のメモリとして注目され、1990年代後半から2000年代前半にかけて、国内外の著名な半導体メーカーが多数研究開発に参入した。しかし、FeRAMは微細加工に多くの課題があり、設計ルール130nmあたりが微細化の限界で、高記憶密度メモリの実現は難しい。2021年時点で、商品化されているFeRAMの集積度は4Mbが最大で、メーカーもRAMXEED, Infineonなど世界で数社に限られている。

フラッシュメモリに比べて、書込み速度は約100倍のDRAM並で、書き換え回数耐性はフラッシュメモリの105回の1億倍の1013回もあり、消費電力が小さい[1]。1999年に富士通が世界に先駆けて実用化したFeRAMは、2006年に非接触ICカードFelicaに採用されるなど、リアルタイムで煩雑にデータ書き換えの起こる用途や、緊急電源オフ時の高速データバックアップ用に広く使用されている[2][3][4]。

【もっと詳しく見る】

FeRAMは、自動運転用車載電子装置などの高速データログ用不揮発性メモリに適しているが、車載用メモリは少なくとも-40~125℃の広い温度領域で動作させる必要がある。標準的なメモリの動作温度上限は75℃~85℃で、動作温度上限を上げるには相応の技術開発が必要になる。

FeRAMは強誘電体の残留分極を利用する。商品化されているFeRAMでは、強誘電体として、チタン酸ジルコン酸鉛(Pb(Zr,Ti)O3: PZT)が使用されている。

【もっと詳しく見る】

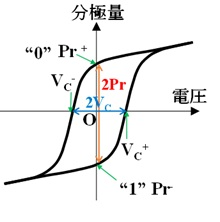

図2に示す強誘電体の分極量と電圧の関係を使い、強誘電体のメモリ動作を説明する。強誘電体の初期状態が、電圧0で分極量Pr-(“1”が書き込まれた状態)にあるとして、正の方向へ電圧を上げていくと、電圧Vc+のとき分極量が0になる。さらに電圧を上げると分極が反転し、反転した分極量が増えていく。その状態から電圧を下げていくと、電圧0で分極量がPr+(“0”の書込み)となり、電圧Vc-で分極量が0となる。さらに、電圧を負方向へ下げていき、再度正方向へ電圧を上げると元の状態 (“1”)に戻る。Pr-とPr+の絶対値を足した値を2Pr、Vc+とVc-の絶対値を足した値を2Vcとそれぞれ定義する。2Prが大きいほど、記憶を保持する能力が高く、2Vcが小さいほど低い電圧でデータを書き換えることができる。一般に温度が高くなると、2Prと2Vcは小さくなり、書込みしやすくなる一方で、記憶を保持しにくくなる[1]。また、発生するリーク電流も大きくなる[7]。

図2 強誘電体の分極量と電圧の関係

強誘電体として広く使用されているPZTは、650℃-750℃の高温熱処理をおこない、結晶(柱状結晶粒)化して分極を発現させる。熱処理時に、耐酸化性貴金属電極の触媒作用で発生した水素による還元作用、あるいは、後の多層メタル配線工程での水素アニールによる還元作用で、PZT中の酸素が抜けて分極量の減少、欠陥発生によるリーク電流が発生する。この現象を防ぐために、厳重に強誘電体を保護膜で包むなど、水素、水の浸入を防ぐ様々な技術が必要になる。

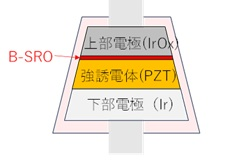

RAMXEEDの開発した強誘電体キャパシタ(FC)の断面構造を図3に示す [8]。強誘電体のPZTを、イリジウム(Ir)下部電極、酸化イリジウム(IrOx (1<x<2))上部電極で挟む一般的な構造に、Bi添加ルテニウム酸ストロンチウム(B-SRO:Bi doped SrRuO3)を挿入している。PZTは、600℃以上で結晶化する必要があるために、耐酸化性のあるIr系電極を用いている。PZTキャパシタでは、上部電極からわずかな量のIrがPZTへ拡散することで、2Vcが下がり、2Prを増加することがわかっている[10]。ただし、このIrの拡散量が多すぎると逆に2Prを下げてしまう。B-SROの厚さを調整することで、Irの拡散量を制御して、FeRAMの動作マージンを上げることができる。また、B-SROは、PZTから上部電極へのPbやO(酸素原子)の拡散を抑制することで、リーク電流を抑制する働きもしている[7][10]。

図3 強誘電体キャパシタの断面構造[8]

(提供:RAMXEED株式会社)

RAMXEEDのFeRAMのメモリセルは図4、5に示すように、チップ全面をFCに展開するCOB(Capacitor-over-bit line)構造を採用している。キャパシタ底のメタル層とキャパシタ上・側面を覆う絶縁層からなる保護層、2層のSiN層とキャパシタ列および2層のメタルプレートでキャパシタ領域を囲む保護ボックス、その外側を囲むキャパシタ列による保護外壁からなる、トリプルプロテクション構造で、PZTが製造プロセスで水や水素によって還元し、分極残留が低下するのを防止している[11]。

図4 メモリセルアレイの平面概略

(文献[11]を参考にして、日本半導体歴史館が作成)

図5 図4のX-X’で示したセルアレイ端の断面概略図

(文献[11]を参考にして、日本半導体歴史館が作成)

PZTは温度が高くなると、残留分極が小さくなり、リーク電流が大きくなるため記憶を保持し難くなる。RAMXEED(旧富士通セミコンダクターメモリソリューション)は、強誘電体コンデンサの構造改良に加えて、PZTを成膜する有機金属気相堆積法(MOCVD)の成膜温度や圧力、分極を発現させるための堆積膜のアニール条件を最適化することで、PZTの結晶性向上と欠陥低減をはかり、125℃でも十分な残留分極を低リーク電流で確保することに成功した。

【もっと詳しく見る】

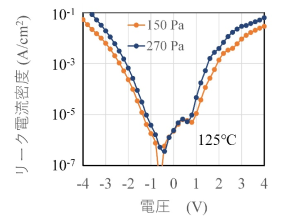

RAMXEEDは、有機金属気相堆積法(MOCVD)を用いて成膜したPZTを酸素雰囲気中でアニールする温度を600℃から700℃に上げて、PZTの結晶性を向上させた。これにより、125℃で測定した2Prが2μC/cm2程度向上した(図6(a))。しかし、常温で測定した2Vcは約0.08 V程度大きくなってしまった(図6(b))。2Vcを小さくするために、PZTの厚さを従来の85nmから75nmに薄くした。強誘電体を薄膜化して実効的な電界を大きくする狙いである。さらに、従来1nmとしていたB-SROの厚さを、ウェーハ面内の均一性を考慮して、2nm以上として十分に余裕をもたせることにした。これらによって、2Vcを最終的に0.4V程度減少させることができた(図7(a)、図7(b))。リーク電流の低減には、MOCVDの圧力を従来の270Paから150Paに下げて、堆積チャンバーでの気相反応を抑制してPZT中の欠陥を減らすことで対応した。図8に成膜125℃で測定したFCのリーク電流密度を示す。リーク電流が大幅に抑制できていることがわかる。

図6(a) 強誘電体成膜後のアニール温度を従来の600℃から700℃としたときの2Pr(125℃測定)

(提供:RAMXEED株式会社)

図6(b) 強誘電体成膜後のアニール温度を従来の600℃から700℃としたときの2Vc(常温測定)

(提供:RAMXEED株式会社)

図7(a) 強誘電体の厚さを従来の85nmから75nmとしたときの2Vc(常温測定)

(提供:RAMXEED株式会社)

図7(b) B-SROの厚さを従来の1nmから2nmにしたときの2Vc(常温測定)

(提供:RAMXEED株式会社)

図8:強誘電体成膜圧力を従来の270Paから150Paとした場合のリーク電流密度対電圧の関係(125℃測定)

(提供:RAMXEED株式会社)

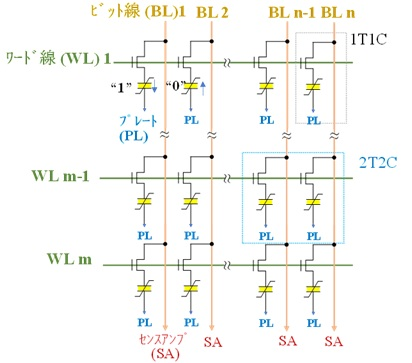

RAMXEEDはこの技術を用いて、2017年に125℃動作256kb FeRAM、2021年に125℃動作4Mb FeRAMの量産に成功した[5](図1)。4Mb FeRAMは、180nm 6層メタル配線CMOSプロセスにより製造され、メモリユニットはデータ保持特性の信頼性が高い2T2C(2トランジスタ2キャパシタ)構成を採用している。

【もっと詳しく見る】

FeRAMは、DRAMとよく似た回路構成で、図9に示すようにDRAMの常誘電体キャパシタを強誘電体キャパシタ(FC)に置き換えた構成になっている。FeRAMでは、プレート(PL)とビット線(BL)を駆動してデータの書込みと読み出しを行う。図9の左上に、FCの分極方向と記憶された値の例を示す。“1”書き込みでは、PLを接地してBLに電圧をかけ、トランジスタ(Tr)をオンにして強誘電体を上向きに分極させる。“0”書き込みでは、PLに電圧を与え、BLを接地する。読み出しでは、PLに電圧をかけ、Trをオンにし、FCに電圧を印加してフローティング状態にしたBLの電位上昇を読み取る。強誘電体の分極が反転する“1”読み出しに比べて反転を伴わない“0”読み出しの方がBLに流れ込む電荷が少ないため、電圧の上昇が小さいことを利用して、“1”と“0”を判別している。

図9 FeRAMの回路構成

(提供:RAMXEED株式会社)

本メモリは、1.8 Vから3.6 Vの広い範囲で動作が可能であり、1013回(10兆回)の書き換えが可能で、125℃までの温度で使用できる。高品質規格AEC-Q100グレード1に準拠しており、車載向けの先進運転支援システム(ADAS)や高性能産業用ロボットに最適である。

図1 車載用4Mb FeRAMの外観[5]

(提供:RAMXEED株式会社)

【補足】

商用化されているFeRAMに採用されている強誘電体PZTにはサイズ効果があり、厚さが100nm以下になると、分極量が急激に減少する。このため設計ルール180~130nm以下の微細化は難しい。

2011年に、HKMGプロセスで使われているHf系酸化物がある条件で結晶化すると強誘電体になり、10nm以下の厚さでも強誘電体の性質を維持することが見つかった。10nm以下に薄膜化してもリーク電流を抑えて強誘電性を維持でき、水素に対する耐性も強いことから、メモリデバイスの微細化を可能にする。高集積不揮発性メモリの実現を目指して、HZO(HfZrO4)を用いる1T1C FeRAMや、HZOをFETのゲート絶縁膜に挿入する1T0C FeFET、強誘電体トンネル接合(FTJ)メモリなどの研究開発が活発化している。AlScN、GaScNなど、数nmの厚さで分極を発現する強誘電体材料も発見され、メモリデバイスは新世代を迎えようとしている[6]。

【参考文献】

- RAMXEED株式会社 ホームページ、"FeRAMについてもっと知る"

https://www.ramxeed.com/jp/tech-column/ - T. Yamazaki, K. Inoue, H. Miyazawa, M. Nakamura, N. Sashida, R. Satomi, A. Kerry, Y. Katoh, H. Noshiro, K. Takai, R. Shinohara, C. Ohno, N. Nakajima, Y. Furumura, and K. Kawamura, "Advanced 0.5μm FRAM Device Technology with Full Compatibility of Half-Micron CMOS Logic device," Proc. Int. Electron Devices Meeting, p. 613-616. (1997), DOI: 10.1109/IEDM.1997.650459.

- 日本半導体歴史館集積回路欄、“2001年:ReRAM混載ICカード用LSIの発売(富士通・松下)”

https://www.shmj.or.jp/museum2010/exhibi714.htm - 富士通株式会社プレスリリース、“FRAM搭載LSIがFeliCa方式ICカードに採用”、(2006年11月7日)

- RAMXEED株式会社プレスリリース、 “車載グレードに準拠した125℃動作の4MビットFeRAM、量産を開始”、(2021年7月6日)

https://www.ramxeed.com/jp/news-and-updates/3375/

【関連文献】

- 小林 正治、“HfO2系強誘電体薄膜を用いた新規メモリデバイス技術の現状と課題”、応用物理、89巻、6号、pp.314-320、(2020)

- W. Wang, K. Takai, K. Nakamura, M. Oikawa, S. Ozawa, K. Nagai, S. Mihara, Y. Hikosaka, H. Saito, M. Kojima, T. Eshita, K. Nomura, H. Yamaguchi "A new electrode structure of IrOx/Bi-doped SrRuO3 for highly reliable La-doped Pb (Zr, Ti)O3-based ferroelectric memories," 22nd Int. Symp. INFOTEH-JAHORINA (INFOTEH) (March, 2023), DOI:10.1109/infoteh57020.2023.

- 王文生 特許第4983172号, 特許第5593935号.

- K. Nomura, W. Wang, K. Nakamura, T. Eshita, K, Takai, S, Ozawa, H. Yamaguchi, S. Mihara, Y. Hikosaka, H. Saito, Y. Kataoka, and M. Kojima, "Reconstruction of IrO2/(Pb, La)(Zr, Ti)O3 (PLZT) interface by optimization of postdeposition annealing and sputtering conditions", J. Appl. Phys., vol. 126, p. 074105 (2019), DOI: 10.1063/1.5091501.

- W. Wang, K. Takai, T. Eshita, M. Nakabayashi, K. Nakamura, M. Oikawa, N. Sato, K. Suezawa, Y. Okita, S. Ozawa, S. Mihara, Y. Hikosaka, H. Saito, and K. Nagai, "Development of a High-Endurance Ferroelectric Capacitor for FeRAM in Automotive and Industrial Applications," Trans. Electron Devices. (early access), doi: 10.1109/ted.2024.3514579.

- H. Saito, T. Sugimachi, K. Nakamura, S. Ozawa, N. Sashida, S. Mihara, Y. Hikosaka, W. Wang, T. Hori, K. Takai, M. Nakazawa, N. Kosugi, M. Okuda, M. Hamada, S. Kawashima, T. Eshita, and M. Matsumiya, “A triple-protection structured COB FRAM with 1.2-V operation and 1017-cycle endurance, ” 2015 IEEE International Memory Workshop (IME) (May, 2015), DOI:10.1109/IMW.2015.7150275.

- T. Eshita, W. Wang, and Y. Hikosaka "Ferroelectric Memory," Elsevier Science, Encyclopedia of Materials: Electronics pp. 218-240 (March 2023), DOI: 10.1016/B978-0-12-819728-8.00042-5.

- W. Wang, K. Nakamura, M. Nakabayashi, T. Eshita, K. Takai, K. Suezawa, M. Oikawa, N. Sato, S. Ozawa, S. Mihara, Y. Hikosaka, H. Saito, and K. Nagai, "A ferroelectric capacitor with an asymmetric double-layered ferroelectric structure comprising a liquid-delivery MOCVD Pb(Zr, Ti)O3 layer and a sputter-deposited La-doped Pb(Zr, Ti)O3 for highly reliable FeRAM," Appl. Phys. Lett. 125, 192901. 2024, doi: 10.1063/5.0230646.

- W. Wang, T. Eshita, K. Takai, S. Amari, K. Nakamura, M. Oikawa, N. Sato, S. Ozawa, M. Nakabayashi, S. Mihara, Y. Hikosaka, H. Saito, K. Inoue, and K. Nagai, "Highly Reliable 4 Mb FeRAM Using a Newly Developed PLZT Capacitor With a Bi-Doped SRO Interlayer." IEEE Electron Device Lett.45, pp 2126-2129,2024, doi: 10.1109/led.2024.3459044.

- W. Wang, T. Eshita, K. Takai, K. Nomura, H. Yamaguchi, K. Nakamura, S. Ozawa, K. Nagai, J. Watanabe, S. Mihara, Y. Hikosaka, H. Saito, and M. Kojima, "An improvement of low temperature characteristics of an La-doped Pb(Zr, Ti)O3 capacitor," Jpn. J. Appl. Phys. vol. 61, (2022), DOI: 10.1109/infoteh57020.2023.

- W. Wang, K. Nakamura, T. Eshita, K. Nomura, K. Takai, H. Yamaguchi, S. Mihara, Y. Hikosaka, H. Saito, and M. Kojima, "Ferroelectric capacitor with an asymmetric double-layer PLZT structure for FRAM, " Appl. Phys. Lett. vol. 120, p. 102901 (2022), DOI: 10.1063/5.0083645.

- W. Wang, K. Nomura, K. Nakamura, T. Eshita, S. Ozawa, H. Yamaguchi, K. Takai, J. Watanabe, S. Mihara, Y. Hikosaka, H. Saito, Y. Kataoka, and M. Kojima, "Ferroelectric random access memory with high electric properties and high production yield realized by employing an AlOx underlying layer of Pt bottom electrode for a La-doped lead zirconate titanate capacitor," Jpn. J. Appl. Phys. vol. 58, p. 016503 (2019), DOI: 10.7567/1347-4065/aae899.

- K. Nomura, W. Wang, H. Yamaguchi, K. Nakamura, T. Eshita, S. Ozawa, K. Takai, S. Mihara, Y. Hikosaka, M. Hamada, M. Kojima, and Y. Kataoka, "Improvement of ferroelectric random access memory manufacturing margin by employing Pt/AlOx bottom electrode for the La-doped Pb(Zr, Ti)O3 ferroelectric capacitor”, Jpn. J. Appl. Phys. vol. 57 p. 11UF01 (2018), DOI: 10.7567/jjap.57.11uf01.

- K. Nomura, W. Wang, H. Yamaguchi, K. Nakamura, T. Eshita, S. Ozawa, K. Takai, S. Mihara, Y. Hikosaka, M. Hamada, M. Kojima, Y. Kataoka, "Effect of Pt/AlOx Bottom Electrode on the Manufacturing Process Margin Improvement of La-Doped Pb(Zr; Ti)O3 Thin Films," 2018 ISAF-FMA-AMF-AMEC-PFM (IFAAP) Joint Conf. (2018).

- W. Wang, K. Nomura, H. Yamaguchi, K. Nakamura, T. Eshita, S. Ozawa, K. Takai, S. Mihara, Y. Hikosaka, M. Hamada, and Y. Kataoka "Control of La-doped Pb(Zr,Ti)O3 crystalline orientation and its influence on the properties of ferroelectric random access memory," Jpn. J. Appl. Phys. vol. 56, p.10PF14 (2017), DOI: doi.org/10.7567/jjap.56.10pf14.

- A. Chen "A review of emerging non-volatile memory (NVM) technologies and applications," Solid-State Electronics, vol. 125, pp. 25–38 ,(2016), DOI: 10.1016/j.sse.2016.07.006..

- T. Eshita, W. Wang, K. Nomura, K. Nakamura, H. Saito, H. Yamaguchi, S. Mihara, Y. Hikosaka, Y. Kataoka, and M. Kojima, "Development of highly reliable ferroelectric random access memory and its Internet of Things applications," Jpn. J. Appl. Phys., vol. 57, p. 11UA01, (2018), DOI: 10.7567/JJAP.57.11UA01.

Ver.001: 2025/7/25