|

|

||||||||||

1980年代後半 DRAMで立体セル構造を採用 〜プロセス技術〜 |

||||||||||

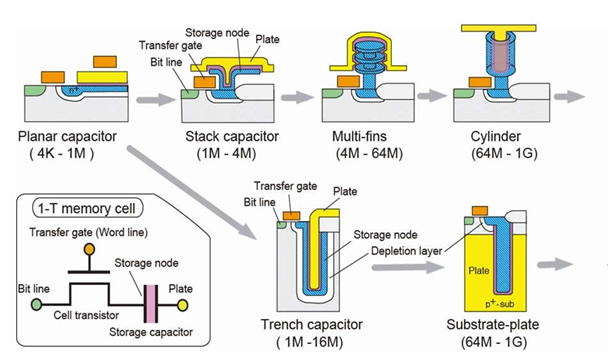

| DRAM(Dynamic Random Access Memory)はキャパシタ(コンデンサ)に電荷を蓄えることにより情報を記憶する素子であり、1970年にインテルにより1KビットDRAMが製品化されてから、一世代約3年毎に4倍に集積度を向上してきた。世代が進む毎にチップ面積を1.4倍に拡大、メモリセルをほぼ1/3に縮小し、集積度4倍化を実現してきた。メモリセル面積を縮小するためには、電荷蓄積キャパシタの面積も縮小しなければならないが、一方で安定なメモリ動作のためにはキャパシタ容量値を保たなければならないので、キャパシタ絶縁膜の厚さを薄くして補ってきた。絶縁膜の薄膜化を可能にするために絶縁膜に印加される電圧を下げる方式も採用された(“ハーフVcc”プレート電圧印加方式)。 1980年代後半のメガビットの時代に入ると、いよいよ、それまでのSi基板表面に平面型MOSキャパシタを形成するプレーナセルでは必要なキャパシタ容量値を確保することができなくなり、立体構造セルが採用されるようになった。立体セル構造としてトレンチセルとスタックトセルがあるが、共に1970年代に日本で発明された。 トレンチセルは、Si基板に垂直な溝を形成してその側壁にキャパシタを形成することによりキャパシタ容量値を確保するセル構造であり、1975年に当時日立の角南英夫により発明され、1982年の国際電子デバイス学会(IEDM)で試作結果が発表された。1980年代後半に、東芝、IBM、シーメンス、TIなどにより、1Mビットで製品化された。 スタックトセルは、スイッチングトランジスタの上に電荷蓄積キャパシタを三次元的に積み上げることにより、キャパシタ容量値を確保するセル構造であり、1976年に当時日立の小柳光正により発明され、1978年のIEDMで試作結果が発表された。製品化は、1985年に富士通が1Mビットで先行し、4Mビットで日立、三菱、三星、金星、現代、Micron、NECが続いた。2000年以降は、微細化に有利なスタックトセルがほとんどのDRAMで採用されている。 スタックトセルを微細化する技術として、容量電極である多結晶Siの表面に凹凸を形成することで単位面積当りの表面積を増加させキャパシタ容量値を増加させるHSG Poly-Si(Hemi-spherical grained Poly-Si)技術も日本で発明された。NECが1990年の国際固体素子・材料コンファレンス(SSDM)でコンセプトを報告し、1992年のIEDMで256Mビット用の技術の一つとして発表、1996年に64Mビットで量産化に成功した。2001年までにDRAMメーカの7割がHSG Poly-Siを採用した。 このように、メガビット世代のDRAMメモリセルの基本技術が日本で発明され、1980年代後半には、生産額シェアにおいても、日本がDRAMの約80%を、全半導体においても50%以上を占めるまでにいたった。 |

||||||||||

DRAMメモリセルの立体構造化 |

||||||||||

|

【参考文献】 1) Hideo Sunami: "The Role of the Trench Capacitor in DRAM Innovation", IEEE Solid-State Circuits Society Newsletter, Vol.13, Issue.1 (2008) 2) 半導体シニア協会ニューズレターNo.59(2008年10月) http://www.ssis.or.jp/ssis/pdf/ENCORE59.pdf 【移動ページ】 プロセス技術/該当年代へ 【最終変更バージョン】 rev.002 2022/8/21 |