|

|

||||||||||

1980擭戙 CAD僣乕儖偺敪払偲EWS壔 乣廤愊夞楬乣 |

||||||||||

| 1980擭偙傠偐傜敿摫懱奺幮偑丄LSI愝寁巟墖偺堊偺榑棟夞楬擖椡丄榑棟僔儈儏儗乕僞丄僞僀儈儞僌専徹丄屘忈僔儈儏儗乕僞丄儗僀傾僂僩CAD乮僼儘傾僾儔儞僫丄帺摦攝抲丒攝慄乯丄儗僀傾僂僩専徹丄儅僗僋惗惉摍偺帺幮EDA僣乕儖傪儊僀儞僼儗乕儉忋偱奐敪丒惢昳揔梡偡傞傛偆偵側偭偨丅 堦曽偱丄屭媞僇僗僞儉惢昳愝寁傪懳徾偲偟偨榑棟夞楬愝寁梡偺CAE(Computer Aided Engineering)僔僗僥儉偲偟偰丄Mentor Graphics幮丄Daisy幮丄Valid Logic幮側偳偺愱嬈偺僣乕儖儀儞僟偑搊応偡傞丅僾儔僢僩僼僅乕儉偵偼Apollo Computer幮惢偺斈梡EWS傪巊梡偟偨傕偺乮Mentor Graphics幮乯偲愱梡偺僴乕僪丒OS傪巊梡偟偨傕偺(Daisy幮丄Valid Logic幮)偑偁偭偨偑丄偦偺屻Sun Microsystems幮偺WS(Work Station)晛媦偺屻丄Linux儀乕僗偺斈梡EWS(Engineering Work Station)偑堦斒揑偵側傞丅偙傟傜偺僣乕儖偼丄榑棟夞楬恾傪擖椡偡傞僌儔僼傿僢僋僄僨傿僞偲偦偺摦嶌専徹傪峴偆榑棟僔儈儏儗乕僞側偳偑堦懱偲側偭偨傕偺偱偁偭偨丅屻偵榑棟夞楬偺扨堦弅戅屘忈傪専弌偡傞屘忈僔儈儏儗乕僞傗丄僞僀儈儞僌専徹傪峴偆僞僀儈儞僌僔儈儏儗乕僞摍傕幚梡壔偝傟偨丅 傑偨丄EWS偺晛媦偵敽偄愝寁幰堦恖傂偲傝偑EWS傗愝寁僣乕儖傪愯桳偟偰巊偆偲偄偆宍懺偑堦斒揑偵側偭偰偔傞丅 儗僀傾僂僩CAD偲偟偰偼丄1985擭Tangent Systems幮惢偺Tangate丄Tancell偑晛媦偟巒傔傞丅儗僀傾僂僩CAD偺僨僼傽僋僩僗僞儞僟乕僪偱偁傞儔僀僽儔儕婰弎僼僅乕儅僢僩LEF乮Library Exchange Format乯傗愝寁忣曬婰弎僼僅乕儅僢僩DEF乮Design Exchange Format乯偑嶌惉偝傟偨丅 1983擭偵偼丄儗僀傾僂僩CAD偱嶌惉偟偨儗僀傾僂僩僨乕僞偺Design Rule Checking(DRC)傗Electrical Rule Checker(ERC)丄儗僀傾僂僩僨乕僞偲榑棟僨乕僞傪斾妑偡傞Layout Versus Schematic (LVS)婡擻傪帩偮ECAD幮偺Dracula偑搊応偡傞乮ECAD幮偼屻偵Cadence幮偵攦廂偝傟偨乯丅傑偨丄嶌惉偟偨儗僀傾僂僩僨乕僞偵偍偗傞婑惗慺巕乮梕検丄掞峈丄僀儞僟僋僞摍乯偺拪弌傪峴偭偰丄偦偺忣曬傪尦偺夞楬偵晅壛偟丄嵞傃夞楬丒榑棟僔儈儏儗乕僔儑儞傪峴偆偙偲偱丄幚嵺偵儗僀傾僂僩偝傟偨夞楬偑惓忢偵摦嶌偟栚揑偺惈擻傪枮偨偡偐偳偆偐傪妋擣偡傞僶僢僋傾僲僥乕僔儑儞媄弍傕敪揥偟丄儅僗僋僨乕僞傪暐偄弌偡慜偵幚暔偵嬤偄宍偱偺夞楬丒榑棟専徹偑峴傢傟傞傛偆偵側偭偨丅 暋悢偺儀儞僟偑偄傠偄傠側僣乕儖傪敪昞偟偨寢壥丄僣乕儖娫偱愝寁僨乕僞偺屳姺偑偲傟側偄摍偺栤戣傕惗偠偰偒偨丅摉帪2戝儀儞僟偱偁偭偨Cadence幮偲Mentor Graphics幮偑偦傟偧傟僼儗乕儉儚乕僋偲偄偆榞慻傒偵懠幮惢昳傪庢傝崬傫偱摑崌偡傞摦偒傕偁偭偨偑惉岟偟側偐偭偨丅偙偺偨傔愝寁僨乕僞傪岎姺偡傞堊偺嫟捠僼僅乕儅僢僩偲偟偰EDIF(Electronic Design Interchange Format)偺尋媶偑丄1983擭偵巒傑傝丄1985擭偵EDIF100丄1988擭偵EDIF200丄1993擭偵EDIF300丄1996擭偵嵟廔斉偺EDIF400偑岞奐偝傟偨丅 |

||||||||||

|

||||||||||

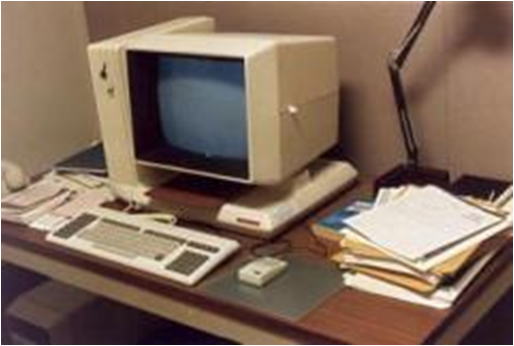

| 恾丂Apollo Computer幮偺EWS Dn3303) | ||||||||||

|

亂嶲峫暥專亃 1) MACMILLEN et al.: AN INDUSTRIAL VIEW OF ELECTRONIC DESIGN AUTOMATION IEEE TRANSACTIONS ON COMPUTER AIDED DESIGN OF INTEGRATED CIRCUITS AND SYSTEMS VOL. 19, NO. 12, DECEMBER 2000 2) 乽EDA (敿摫懱)乿亀僼儕乕昐壢帠揟僂僀僉儁僨傿傾擔杮岅斉亁乮2010擭10寧14擔8:41乯 http://ja.wikipedia.org/wiki/EDA_(敿摫懱) 3) 乽Apollo Computer乿亀僼儕乕昐壢帠揟僂僀僉儁僨傿傾塸岅斉亁乮2010擭9寧10擔6:12乯 http://en.wikipedia.org/wiki/Apollo_Computer 亂堏摦儁乕僕亃 廤愊夞楬/奩摉擭戙傊 亂嵟廔曄峏僶乕僕儑儞亃 rev.001 2010/10/26 |